## The Silicon Valley Career of a UIUC Physics Ph.D.

Alan Stivers, Ph.D. UIUC, 1979

# None of the work I will describe was done without the help and advice of many, many people.

Alan Stivers, 8/23/2019

### Outline

- Introduction: me, you and my employer

- Forces driving my career

- My first job

- Technology transfer problems

- Case study: Resolution of transfer problems and the after-effects

- Overall learning

- Q&A

#### Me

- Grew up in Silicon Valley

- Physics Education: AB at UC Berkeley, MS and PhD at UIUC

- Ph.D. advisor: Prof. C. T. Sah

- Intel Career: 1979 to 2008

- Started in Quality Assurance doing Voltage Contrast Electron Beam Probing

- Moved to Components Research (CR) to do advanced process development

- Chemical vapor deposition of polycrystalline-Si, Si<sub>3</sub>N<sub>4</sub>, TiSi<sub>2</sub>

- Multichip packaging

- Silicon selective epitaxial deposition

- Advanced silicides

- Alternating phase-shift masks for 193nm lithography

- Extreme ultra-violet masks for 13.4 nm lithography

- Things you learn always carry forward. They are all arrows in your quiver.

## You, from my perspective

- You are being groomed to be the sharp end of the spear that advances science and technology.

- You may become the person that points that spear where it does the most good.

- People with our training often start out as individual contributors, but often transition to leading other people.

- You will find:

- A big future for science and technology. The show is only starting.

- Later in your careers, technology will start to catch up with the physics you learn in grad school.

- Relationships matter, including the ones you make here.

## My Employer for 28 Years: Intel Corporation

- Founded in 1969 by Gordon Moore and Robert Noyce

- Key inventions: Si gate SAMOS (at Fairchild), dRAM, EPROM,  $\mu$ P

- Employees: 15k in 1979, 84k in 2008, 107k today

- Annual revenue: \$69B today

- Highly disciplined culture

- Get lots done but not for everyone

- Great management IMHO: "Conviction Required" philosophy

- I was lucky to be there during its growth.

#### Two Driving Forces in my Career

- Decision Making Using the Scientific Method

- Test hypotheses with data.

- Unsaid: beware of opinions, especially those expressed forcefully.

- Modified in industry: restricted to internally accepted practices and standards.

- Standardization restricts decision space but simplifies and <u>speeds</u> decision making.

- Makes maximum use of an organization's knowledge base

- Key Benefit: Allows easy insertion of new learning into that knowledge base

- Semiconductor Scaling, *i.e.*, You Always Can Do Better!

- Smaller means faster: higher current drives lower capacitance

- More applications and sales

- Smaller means cheaper: more product per wafer means lower cost per product

More applications, sales and profits

- Smaller means you need fewer factories to supply the market

- \$5B to \$10B savings up front if one factory doesn't need to be built

- More jobs for engineers to work on faster scaling

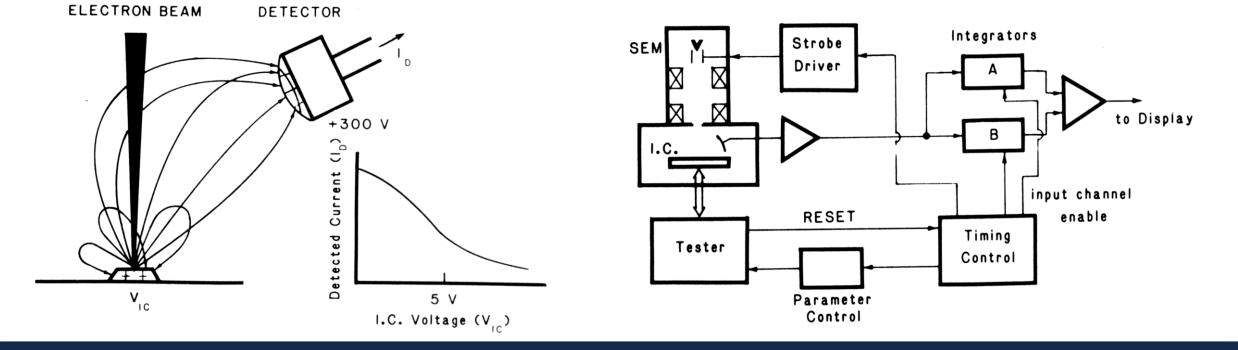

#### My First Job: Voltage Contrast Electron Beam Probing

Sample voltage affects secondary emission: +V pull electrons away from detector  $\rightarrow$  dark electron image Stroboscopic electron beam control for freeze action images of operating circuit

#### **Voltage Contrast Applications**

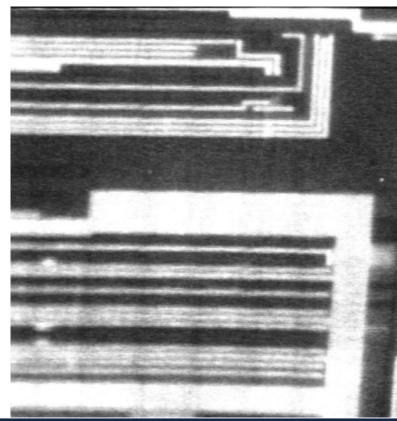

#### Stroboscopic VC freezes action on an operating 80286

Stroboscopic image

# LSM

Alan Stivers, 8/23/2019

Logic State Map:

x-axis time, y-axis space

#### Accomplishments

- Working with Quality and Reliability Engineers

- Failure analysis of several products

- Working with Chip Designers

- Identification of design defects in logic circuits

- Identified the last design error keeping Intel's then lead product, the 80286, from release (1982 at 8MHz clock).

- My lab then moved to be in the same building as the chip designers.

- Identified speed limiting elements of logic circuits

- > Enabled higher speed versions (to 12.5 MHz) to be released.

#### Learning from this project

- A new technique is only as powerful as its application

- My customer's application was Intel's then lead product, 80286.

- Measurement is only one part of the solution

- You need the expertise and resources of your customers

- Be close to your customers

- Even being across the street hinders application

- Always be ready to go the extra mile. Their deadlines are your deadlines.

- Learning enabled a successful electron beam-based repair technology for alternating phase-shift masks 15 years later for Intel's 65nm process.

## Intel Technology Transfer Problem History

- At Fairchild: R&D-to-manufacturing transfer problems

- At Intel

- 1. Do R&D in the factory:

- Plus: no transfer needed Minus: R&D lowered product output

- 2. R&D done in separate factory and Copy Exactly transfer methodology begun

- Large R&D lab/factory

- Process, toolset, materials, procedures, specs all copied exactly to manufacturing.

- Very successful

- 3. Later, D became more difficult. Need to do more advance work

- Pathfinding (advanced development) started to look at next technology generation.

- Components Research (CR) started to look several generations out.

- Again needed to solve the problem: how to transfer R to D?

## Case Study of a Successful R $\rightarrow$ D Transfer

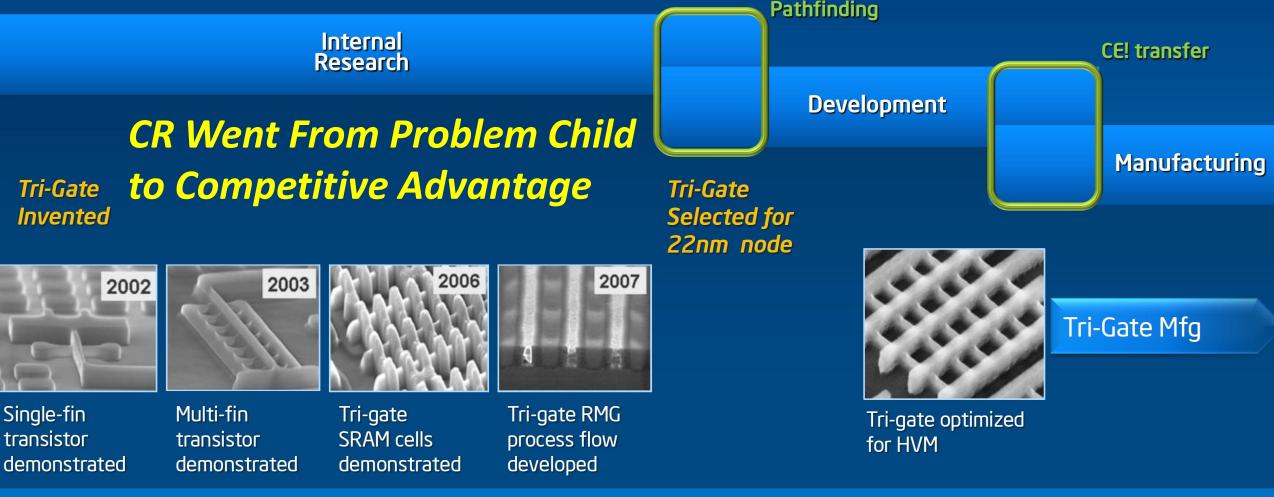

- At first, Components Research (CR) had difficulty transferring results to Technology Development (TD). CR perceived as a problem child.

- Management puts CR and TD under the same senior manager.

- CR must "sell" its projects to TD.

- My boss and I decided on an advanced silicide project and this was approved by TD.

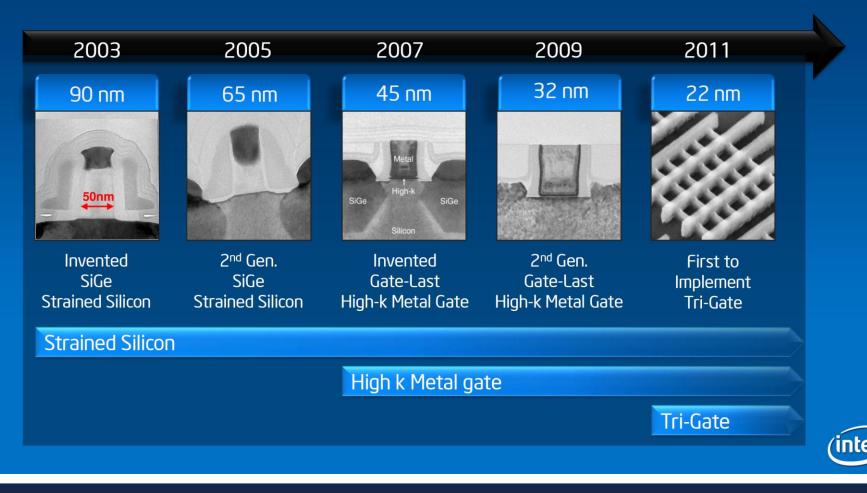

- There were early signs of scaling limits in the then current TiSi<sub>2</sub> process.

- We decided to explore:

- New materials/same process: NiSi, PdSi and PtSi

- Same material/new process: Selective TiSi<sub>2</sub> Chemical Vapor Deposition

- Got TD OK along with agreement on key qualities to optimize

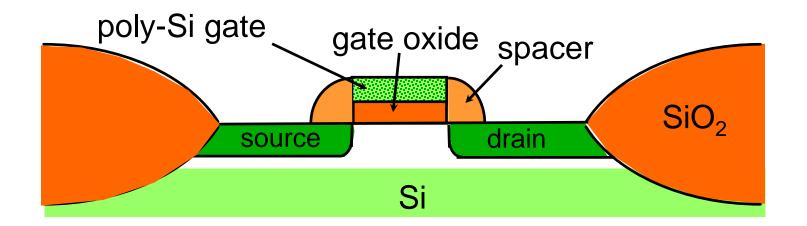

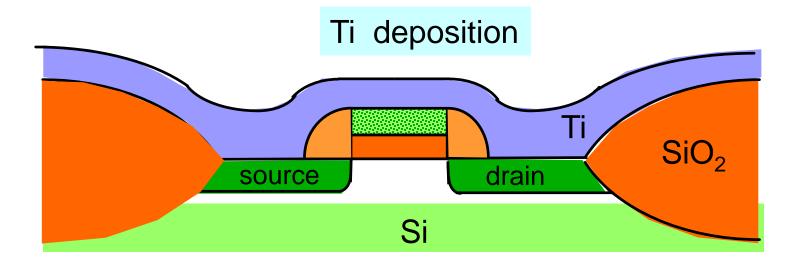

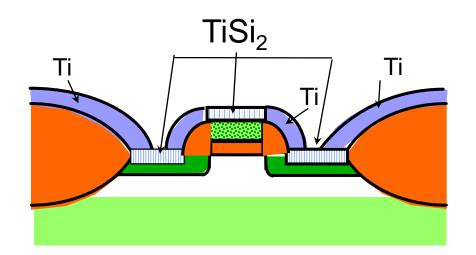

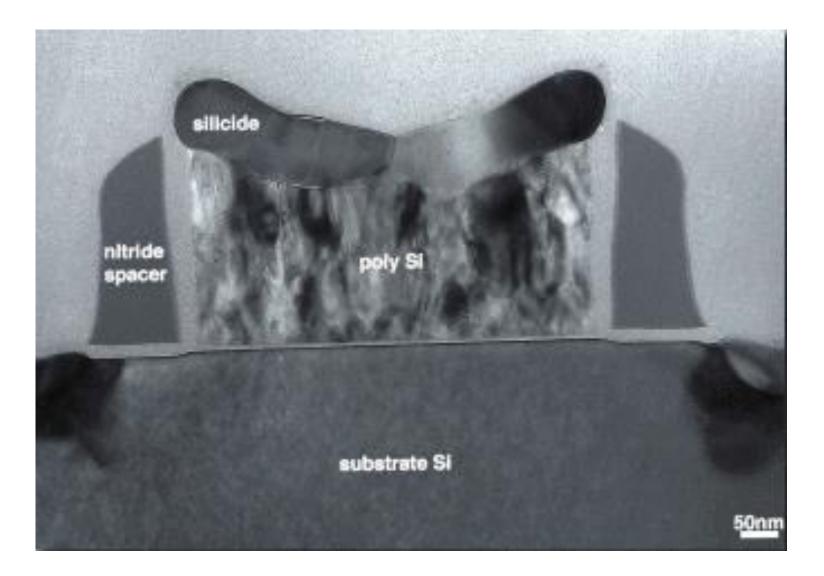

#### **Self-Aligned Silicide (SALICIDE) Process Flow**

Heat treatment reacts Ti with Si No reaction with  $SiO_2$  or SiN Get TiSi<sub>2</sub> only over S/D and gate

SELF-ALIGNED PROCESS! SCALABLE!

Selective etch to remove only unreacted Ti. Use  $H_3PO_4$

- Metal silicides are metallic.

- They lower the sheet resistance of S/D and the poly-gate

- Lower resistance  $\rightarrow$  Higher current  $\rightarrow$  Faster circuit

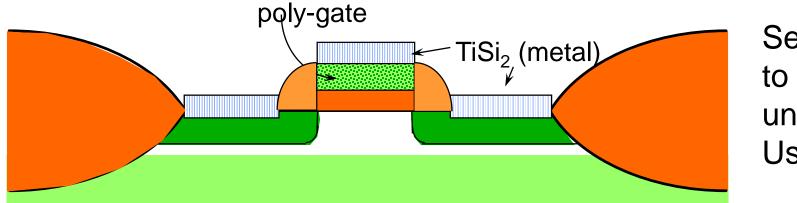

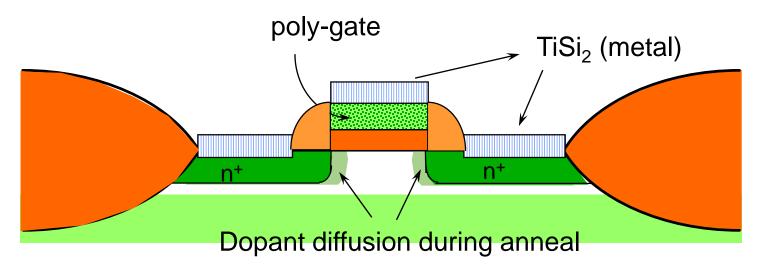

#### Issue: Anneal required for low-resistivity TiSi<sub>2</sub> structure transition

- TiSi<sub>2</sub> C49-to-C54 crystal structure transition requires a thermal anneal.

- Done after S/D formation diffusion softens junction edges and lowers performance → 10% performance loss on 180nm generation n-channel devices.

- Transition needs longer/hotter anneal as line width approaches TiSi<sub>2</sub> grain size

- SCALING LIMIT! Need to find a new alternative.

#### **Ti Salicide Gate and Source/Drain**

#### **Quick Project History and Information Flow 1**

- Initial requirements provided by TD

- Narrowed down options in our California lab using materials measurements. NiSi worked best in our test devices.

- Developed a basic NiSi process in California with the help of Applied Materials.

- Weekly flights to TD site, attended meetings, reviewed data, lunch, one-on-one discussions. Developed a trusting relationship with TD

- Began to understand current process and speed of change at TD

- High rate of learning means understanding of requirements always changing

- The goalposts are always moving!

Alan Stivers, 8/23/2019

$TD \rightarrow CR$

$TD \rightarrow CR$  $TD \rightarrow CR$

#### **Quick Project History and Information Flow 2**

- Ran simple experiments at Development site to quantify performance loss due to salicide anneal of TiSi<sub>2</sub>. Quantified scaling limit.

- Ran NiSi experiments at the Development site using our NiSi process inserted into the Development process. Used their tools and testing and compared against Development controls. Demonstrated 15% performance improvement vs. 30% overall TD performance goal.

- Development adopts NiSi as a worthwhile option.

- A research engineer (not me) is transferred to Oregon to continue the development

$D \rightarrow R \rightarrow D$

$R \rightarrow D$

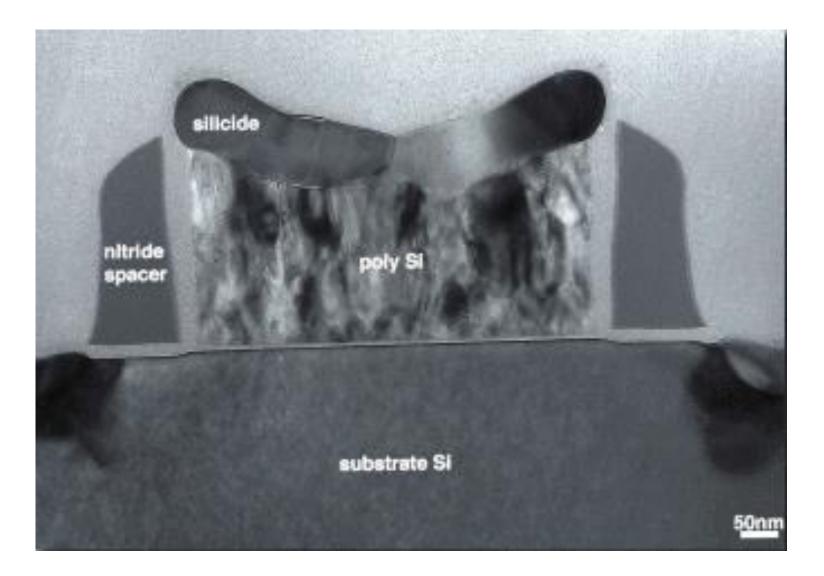

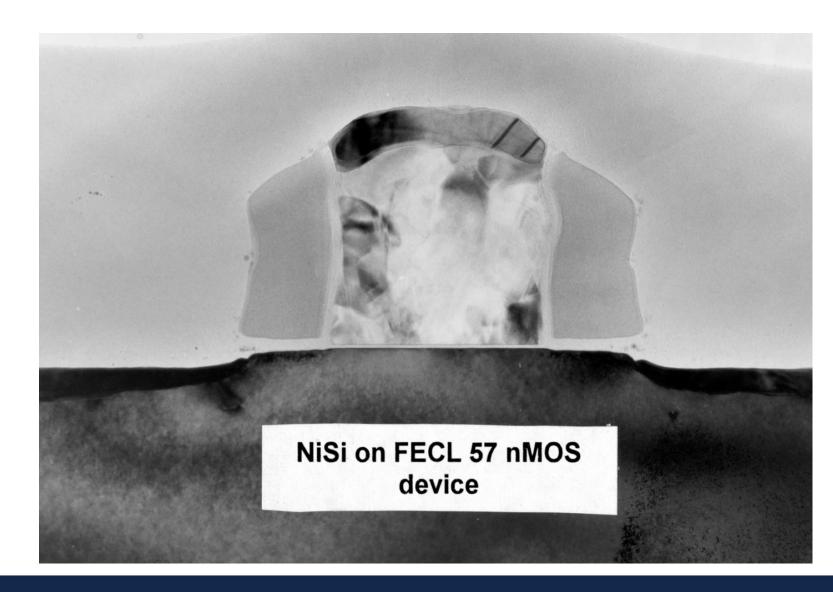

#### TEM x-section of early device with NiSi

- Test device designed for TEM cross-section.

- Good silicide formation on S/D and gate using a low temperature process.

- From 1997 on older process (250 nm node)

#### **Ti Salicide Gate and Source/Drain**

#### Intel Corporate Response to this Work

- Development spent 4+ years developing a high-yield NiSi process.

- CoSi<sub>2</sub> used in 180nm and 130nm technologies, a process acquired when Intel bought Digital Equipment Corp to settle a patent dispute.

- NiSi was first used in manufacturing in the 90nm technology.

- NiSi was preferred over CoSi<sub>2</sub> due to its compatibility with SiGe used in raised source/drain process and the strained Si process.

- This was impossible to predict when we started.

- Organizational Change: Most of CR moved to Oregon to work closely with TD (1997-8)

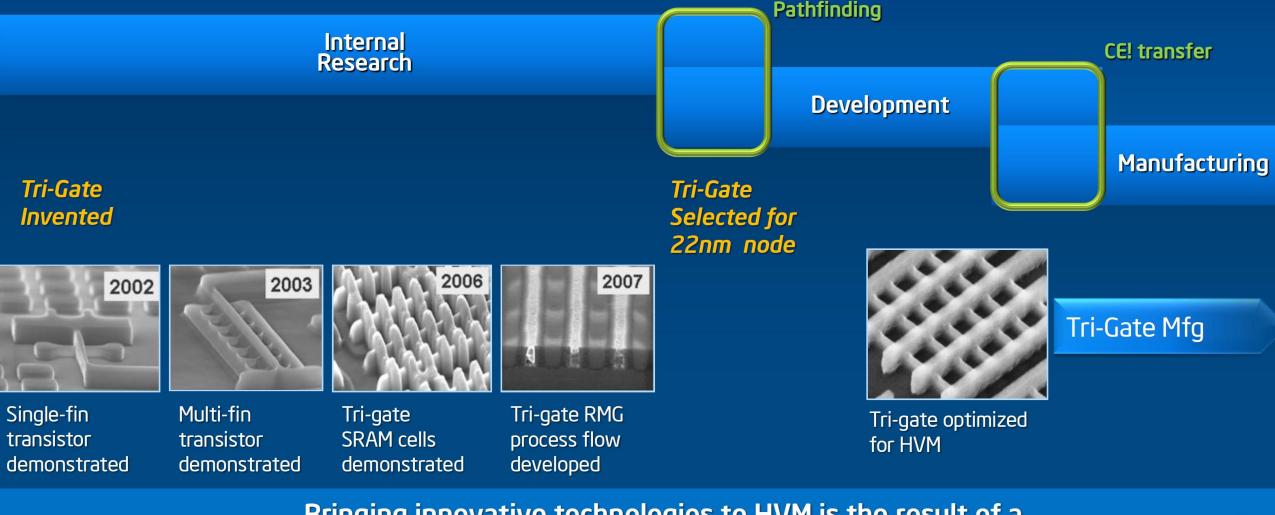

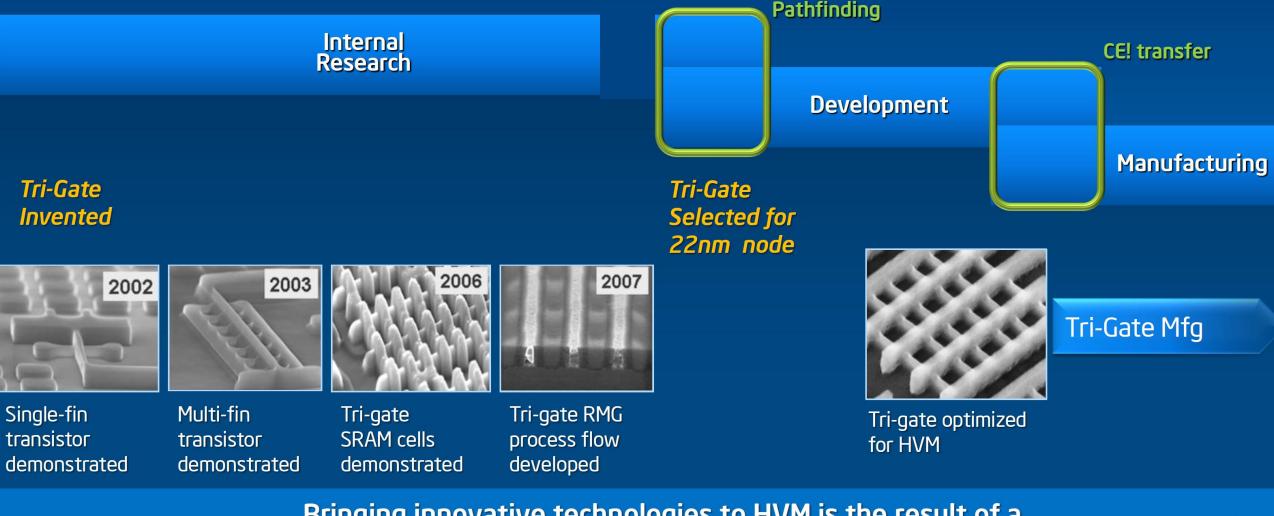

- Subsequent big CR contributions in high-k dielectric (45 nm technology) and tri-gate process (FINFET, 22 nm process)

#### **NiSi in Manufacturing**

<u>90nm/65nm nodes</u>: NiSi on SiGe S/D and gate <u>45nm/32nm nodes</u>: NiSi on SiGe S/D. Metal gate

over high-k dielectric requires no silicide.

<u>22nm node</u>:

No silicide used on trigate device.

#### Transistor Innovations Enable Technology Cadence

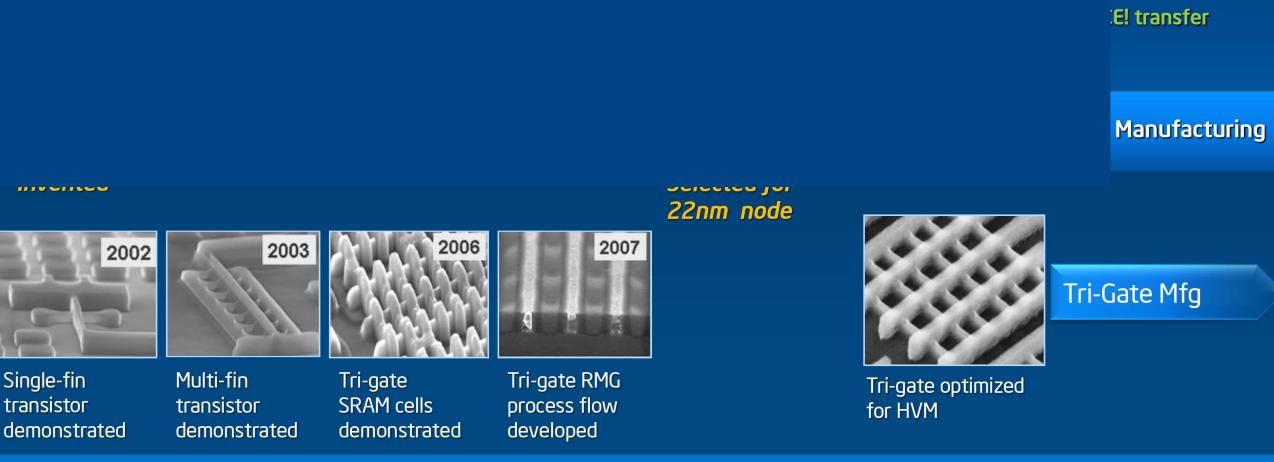

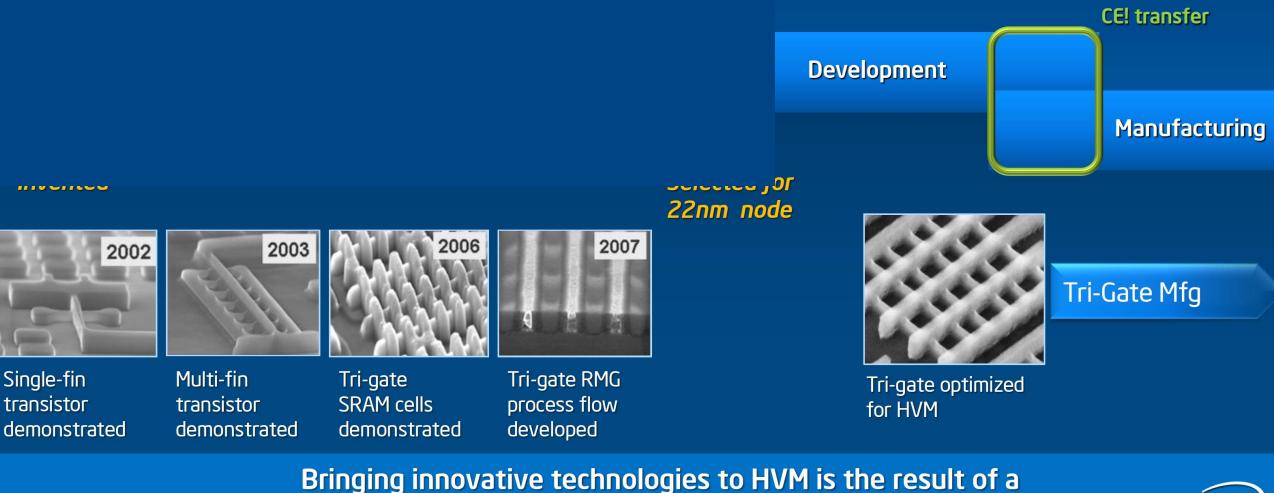

# From 2011Tri-Gate Achievement Results from<br/>Long Term Commitment to Research

Bringing innovative technologies to HVM is the result of a highly coordinated internal research-development-manufacturing pipeline

#### From 2011 Tri-Gate Achievement Results from Long Term Commitment to Research

Bringing innovative technologies to HVM is the result of a highly coordinated internal research-development-manufacturing pipeline

(intel)

# From 2011Tri-Gate Achievement Results from<br/>Long Term Commitment to Research

Pathfinding

highly coordinated internal research-development-manufacturing pipeline

# From 2011Tri-Gate Achievement Results from<br/>Long Term Commitment to Research

Bringing innovative technologies to HVM is the result of a highly coordinated internal research-development-manufacturing pipeline

(intel)

#### Tri-Gate Achievement Results from Long Term Commitment to Research

From 2011

Bringing innovative technologies to HVM is the result of a highly coordinated internal research-development-manufacturing pipeline

#### Some theories on why transfers from R to D fail

- Staff falls short:

- Research engineers not doing a complete enough job

- Trying to do a "complete" job will ensure your failure

- Research engineers not working hard enough

- Researchers cannot schedule progress. Work on several options.

- Organization or management falls short:

- Administrative barriers and organizational territoriality

- Dislike or distrust between members of different organizations.

- "Not invented here" attitude on the part of the receiving organization.

- Buzzword-dependent theories:

- People or organizations not "entrepreneurial" enough.

#### At least at Intel, all untrue

#### Key Methods for Success

- Understand and adopt the customer's methods, especially their decision-making process

- No one really has the time to redo results, so just do it their way.

- Transfer information, not a finished process or product

- Enable your customer to finish the process or product.

- Work constantly at transferring intermediate research results and getting *feedback* to direct future research.

- Extract learning from research work that the customer does not adopt.

- Example: Selective CVD TiSi<sub>2</sub> learning aided selective CVD SiGe development.

- Shamelessly use your contacts and your UIUC pedigree.

## Learning to Lead

- Leadership is learned over many years. It is most critical and beneficial when working across organizations.

- A leader is simply a servant with a vision.

- Help solve their problem.

- Spend lots of time with your customers to learn what they know and how they did it, to develop trust and communicate your vision.

- Leadership is way more interesting than authority. Don't confuse the two.

- You can start serving and leading on Day One.

- You need to take responsibility for the transferability of your work.

- Capable people are willing to help with a good new idea.

- Your co-workers and managers value leadership.

- Everyone in this room should expect to lead at some point.

# Thank you for your attention

Alan Stivers, 8/23/2019